|

FirFirGCD Application

|

|

FirFirGCD Application

|

Hepsycode is a prototypal tool to improve the design time of embedded applications. It is based on a System-Level methodology for HW/SW Co-Design of Heterogeneous Parallel Dedicated Systems. The whole framework drives the designer from an Electronic System-Level (ESL) behavioral model, with related NF requirements, including real-time and mixed-criticality ones, to the final HW/SW implementation, considering specific HW technologies, scheduling policies and Inter-Process Communication (IPC) mechanisms. The system behavior modeling language introduced in Hepsycode, named HML (HEPSY Modeling Language), is based on the Communicating Sequential Processes (CSP) Model of Computation (MoC). It allows modeling the behavior of the system as a network of processes communicating through unidirectional synchronous channels. By means of HML it is possible to specify the System Behavior Model (SBM), an executable model of the system behavior, a set of Non Functional Constraints (NFC) and a set of Reference Inputs (RI) to be used for simulation-based activities. Through the execution of different steps, including a system-level Design Space Exploration (DSE) approach that allows the related co-design methodology to suggest an HW/SW partitioning of the application specification and a mapping of the partitioned entities onto an automatically defined heterogeneous multi-processor architecture, it is possible to proceed with system implementation.

Hepsycode uses Eclipse MDE technologies, SystemC custom simulator implementation and an evolutionary genetic algorithm for partitioning activities, all integrated into an automatic framework that drive the designer from first input to final solution.

GNU GENERAL PUBLIC LICENSE Version 3, 29 June 2007 (see gpl-3.0.en.html)

We currently support:

Email:

(please take care to use [HEPSYCODE SUPPORT] as object

Research publications are available on Hepsycode Website and Publications

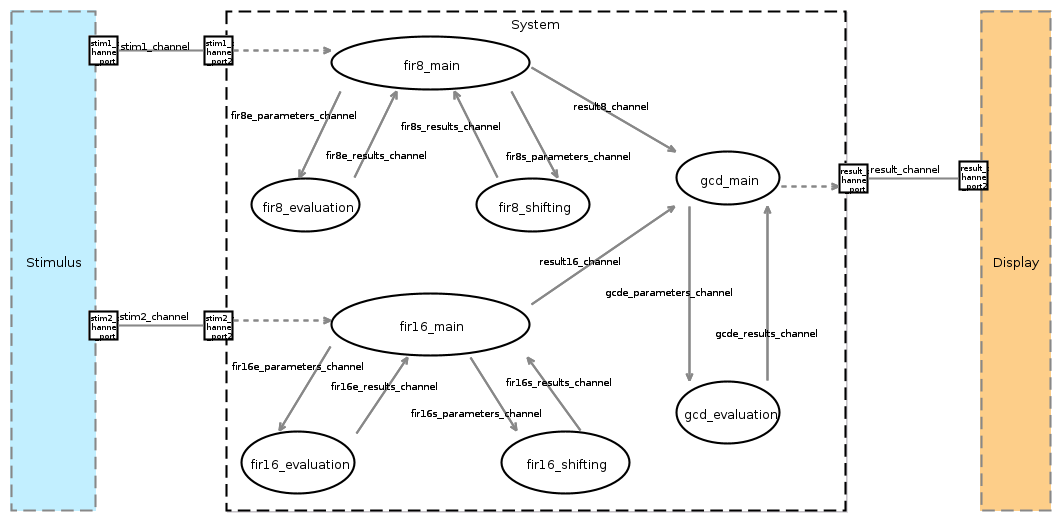

We provide an example Hepsycode project, called FirFirGCD (FFG). FFG is a synthetic application that takes in input pairs of values (triggered by Stimulus), makes two filtering actions (FIR8 and FIR16) and then makes the Greatest Common Divisor (GCD) between the filters outputs and displays the result. This application is composed of three main components: 2 Finite Impulse Response (FIR) digital filters and a Greatest Common Divisor (GCD) component, as show in the figure below.

More details can be found at the link: www.hepsycode.com